MIPS Technologies stellt neue Mikroprozessor-Cores der Aptiv(TM)-Generation vor

Höhere Leistungsfähigkeit mit den neuen microAptiv(TM)-, interAptiv(TM)- und proAptiv(TM)-Prozessoren

(IINews) - Wesentliche Leistungsmerkmale:

-Neue Generation von Prozessor-Cores bietet hohe Leistungsfähigkeit für Anwendungen in den Bereichen Home Entertainment, Netzwerk-technik, Mobilfunk und Embedded-Systeme

-Hochleistungsfähiger proAptiv(TM)-Core erzielt beste CoreMark/MHz-Werte aller lizenzierbaren IP-Cores, zusammen mit bester Flächeneffizienz

-Multi-threaded interAptiv(TM)-Core bietet hohe Leistungseffizienz und erreicht höhere CoreMark/MHz-Werte als andere Cores mit ähnlich großer Die-Fläche

-Hocheffizienter microAptiv(TM)-Core erzielt höchste CoreMark/MHz-Werte unter allen Cores der Mikrocontroller-Klasse; zusammen mit DSP-Beschleunigung und Sicherheitsfunktionen

-Bereits mehrere große Lizenznehmer für die Aptiv(TM)-Cores gewonnen

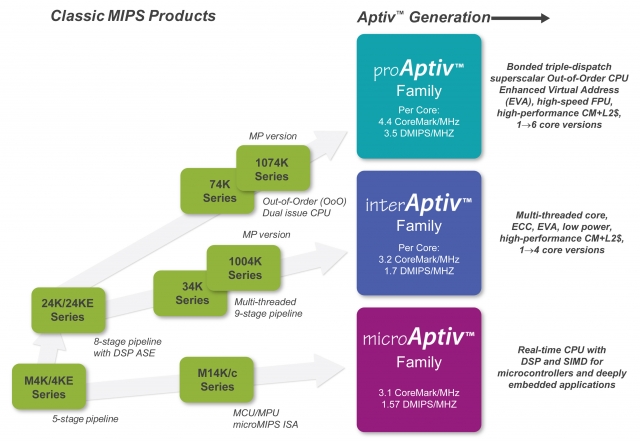

SUNNYVALE, Kalif. - 10. Mai 2012 - MIPS Technologies stellt mit der Aptiv-Generation neue Mikroprozessor-Cores vor. Die proAptiv, interAptiv und microAptiv Cores bieten drei verschiedene Leistungsstufen für Anwendungen im gesamten MIPS-Zielmarkt.

Alle Cores basieren auf der MIPS32® Release 3 Architektur und bauen auf MIPS" führender Stellung im Bereich Home Entertainment auf. Sie stärken die Position im Bereich Netzwerktechnik, erweitern MIPS" Angebot für den hochvolumigen Embedded-Markt und stellen eine äußerst wettbewerbsfähige Alternative für die Entwicklung von Mobilfunkanwendungen dar. Für Mobilfunkgeräte bietet die Aptiv-Generation hohe Multicore-Performance für Apps auf Tablets und Smartphones, effiziente Multi-threading-Technologie für Basisbandprozessoren und Entry-Level Performance für Embedded-Steuerungen und -Anwendungen wie Touchscreen-Controller, SIM/Sicherheit und GPS.

Leistungsmerkmale der proAptiv-Cores:

-Highend-CPU-Leistungseffizienz mit über 4.4 CoreMark/MHz und

3.5 DMIPS/MHz (1) auf einer wesentlich kleineren Die-Fläche als bei anderen IP-Cores (2)

-Ideal für Anwendungen (Apps) auf vernetzten Consumerelektronik-geräten wie Smartphones, Tablets und "Smart"-Home-Entertainment-Geräten sowie für die Control-Plane-Verarbeitung in der Netzwerktechnik

-Effiziente Highend-Leistung minimiert den Bedarf an ausgefallenen Power-Management-Systemen wie "big.LITTLE" in vielen mobilen Anwendungen

-60-75% mehr Leistung bei CoreMark- und DMIPS-Werten als bei MIPS32 74K?/1074K?-basierten Superscalar-Single-/Multicore-Produkten

-Hochskalierbare Lösung nutzt einen oder mehrere Threads pro Core und bis zu sechs Cores, die in einem Multicore-CPS (Coherent Processing System) miteinander verbunden sind

- Wesentliche Architekturmerkmale und Verbesserungen:

oHochleistungsfähige Multi-Issue-, Deeply Out-of-Order (OoO) Architektur mit Branch-Prediction

oNeue, leistungsfähigere Fließkommaeinheit (FPU) mit hoher synthetisierbarer Frequenz für 1:1-Takt mit Core- und nativer Double-Precision-Ausführung

oSingle-/Multicore-Konfigurationen (bis zu sechs Cores)

oVerbesserter, integrierter Coherence Manager der zweiten Generation und L2-Cache-Controller mit geringerer Latenz

oMIPS-Digitalsignalverarbeitungs-(DSP) Application Specific Extension (ASE) v2

oEnhanced Virtual Address (EVA) für effiziente 32-Bit-Adress-Map-Nutzung, um einen 3GB+ User-Space zu erzielen

Leistungsmerkmale der interAptiv-Cores:

-Der interAptiv-Core nutzt eine ausgewogene 9-stufige Pipeline mit Multi-threading, liefert hohe Leistung und erzielt einen um 50% besseren CoreMark/MHz-Wert als andere Cores mit ähnlich großer Die-Fläche (1,2)

-Ideal für hoch-parallele Anwendungen, die eine Kosten- und Leistungsoptimierung erfordern, wie Smart Gateways, Basisband-verarbeitung in LTE-Endgeräten und kleinen Zellen, SSD-Controller und Automobilelektronik

-Die hochskalierbare Lösung nutzt einen oder mehrere Threads pro Core und bis zu vier vernetzte Cores in einem Multicore-CPS (Coherent Processing System)

- Leistungsmerkmale und Verbesserungen:

oMulti-threaded Pipeline implementiert virtuelle Dual-Prozessoren, die als zwei vollständige CPUs auf einem SMP-Linux-Betriebssystem erscheinen

oHardware Quality of Service (QoS), Thread-Management-Support und Inter-thread-Kommunikation ermöglichen eine optimale Steuerung von Echtzeit-Anwendungen

oVerbesserter, integrierter Coherence Manager der zweiten Generation und L2-Cache-Controller mit geringerer Latenz

oSupport für bis zu zwei I/O-Kohärenzeinheiten

oPower-Management-Funktionen auf Core- und CPS-Ebene

oECC-Support (Error Checking and Correction) im L1-Daten-Cache, L2-Cache und Daten-SPRAM

oEnhanced Virtual Addressing (EVA) für effiziente 32-Bit-Adress-Map-Nutzung, um einen 3GB+ User-Space zu erzielen

oOptionale Fließkommaeinheit

Leistungsmerkmale der microAptiv-Cores:

-Stromsparender, kompakter Echtzeit-Embedded-Prozessor-Core mit integrierten Standard-I/Os, der auf der bewährten MIPS32 M14K(TM) Core-Familie mit microMIPS(TM) Code-Compression-Befehlssatz-Architektur aufbaut

-Integriert DSP- und SIMD-Funktionen für Signalverarbeitungs-anforderungen in verschiedenen Embedded-Bereichen wie industrielle Steuerungen, Smart Meter, Automotive und leitungsgebundene / drahtlose Kommunikationstechnik

-Nutzt eine 5-stufige Pipeline und erzielt 3.09 CoreMark/MHz und 1.57 DMIPS/MHz (1) im microMIPS-Modus mit 40% bzw. 25% höherer Leistung im Vergleich zu anderen Cores (2)

-MCU- und MPU-Versionen (mit integriertem Cache-Controller/MMU) für Mikrocontroller- und Embedded-Anwendungen erhältlich

-Im Vergleich zu früheren Generationen von MIPS-Cores und Cores des Wettbewerbs stehen nun mehr Funktionen für Steuerungs- und DSP-Anwendungen zur Verfügung

-Neue Speicherschutzeinheit (Memory Protection Unit) für Programmcode- und Datensicherheit, microMIPS-exklusiver Ausführungsmodus, sicheres Debugging und 2-Draht-cJTAG-Support

Über den CoreMark(TM)-Benchmark:

Der von EEMBC entwickelte CoreMark-Benchmark ist ein einfacher aber doch anspruchsvoller Benchmark, der speziell zum Testen der Leistungsfähigkeit von Prozessor-Cores entwickelt wurde. Ein CoreMark-Durchlauf erzeugt einen Zahlenwert, mit dem Anwender verschiedene Prozessoren schnell untereinander vergleichen können. Weitere Informationen unter: http://www.coremark.org.

Produktspezifikationen und Details:

Detaillierte Produktinformationen, einschließlich Benchmarks, Spezifikationen, Datenblätter etc. unter: www.mips.com/aptiv.

Verfügbarkeit:

Alle Aptiv-Core-Familien können ab sofort lizenziert werden. Die proAptiv-Familie wird ab Mitte 2012 allgemein zur Verfügung stehen und unterstützt eine Reihe von Funktions- und Leistungsanforderungen mit Single- und Multicore-Versionen. Die neue proAptiv FPU steht ebenfalls zur Verfügung. Die interAptiv-Familie wird ab Mitte 2012 in Dual- und Quadcore-Konfigurationen mit einer optionalen FPU erhältlich sein. Single-Core-Versionen wird es ab dem vierten Quartal 2012 geben. Die microAptiv-Familie ist ab sofort als Cache/MMU-Version oder als Core ohne Cache verfügbar. Weitere Informationen über die Produktverfügbarkeit unter info(at)mips.com oder unter www.mips.com/aptiv.

Anmerkungen:

(1) Die Dhrystone-2.1- und CoreMark-1.0-Werte wurden mit der Mentor Sourcery CodeBench v2011.03-94, gcc 4.5.2 erzielt.

(2) Basierend auf den veröffentlichten Werten von ARM; CoreMark Scores von der EEMBC-CoreMark-Website und aus Material, das über das Internet erhältlich ist.

Zitate:

"Mit der Einführung unserer neuen Aptiv-Generation begibt sich MIPS in eine neue Ära der Innovation und steigert seine Wettbewerbsfähigkeit. Die Aptiv-Generation basiert auf strategischen Investitionen und weist den Weg in die Zukunft. Wir steigern die Leistungseffizienz auf ein neues Niveau. Unsere vorherigen Core-Generationen waren bereits leistungseffizienter als der Wettbewerb. Die neue Aptiv-Generation ist sogar noch besser. Mit diesen Cores und dem immer größer werdenden Ecosystem rund um die MIPS-Architektur bieten wir Lösungen, mit denen unsere Kunden sich im immer wettbewerbsintensiveren Markt differenzieren können."

-Gideon Intrater, Vice President Marketing, MIPS Technologies

"Wir gratulieren MIPS zu den neuen Aptiv Prozessor-Cores. Die Multi-Threaded Technologie von MIPS hat großartige Ergebnisse für die Gateway Lösungen von Lantiq erzielt - Maximierung der Leistung bei Minimierung von sowohl Energieverbrauch als auch Systemkosten. Unsere Gateway Lösungen adressieren Systemkonfigurationen von kostenoptimiertem Fast Ethernet bis hin zu funktionsreichen hochleistungsfähigen Gigabit Ethernet Systemen. Sie sind konzipiert, um die xDSL Services der Telekom Carrier im weltweiten Markt zu verbessern und auszubreiten. Mit den Lantiq Gateway Lösungen können Betreiber die steigende Nachfrage nach Triple-Play Services und In-Home Gigabit Durchsatz mit erheblichen Einsparungen bei Kosten, Größe und Energie erfüllen, ohne Kompromisse bei der Systemleistung."

-Rainer Spielberg, Vice President of Marketing, Lantiq

"Die vorläufigen CoreMark-Benchmark-Ergebnisse, die MIPS für seinen neuen proAptiv-Core veröffentlicht, zeigen, dass eine Deeply-Pipelined-CPU nicht unbedingt von den Steuerungsbefehlen innerhalb des CoreMark benachteiligt wird. EEMBC entwickelte den CoreMark als eine realistische Messmethode für die CPU-Leistungsfähigkeit, anstatt sich auf ineffiziente Alternativen wie DMIPS zu verlassen. Wir freuen uns auf MIPS" Support für den CoreMark als neuen Standard zur Messung der grundlegenden CPU-Performance und gratulieren MIPS zu den erzielten neuen Leistungswerten."

-Markus Levy, President, EEMBC

Themen in diesem Fachartikel:

Unternehmensinformation / Kurzprofil:

Über MIPS Technologies (www.mips.com):

MIPS Technologies, Inc. (Nasdaq: MIPS) ist ein führender Anbieter von branchenweit standardisierten Prozessorarchitekturen und Cores. MIPS-basierte Designs sind bereits in vielen bekannten Produkten aus den Bereichen Home Entertainment, Kommunikation, Networking und tragbare Multimediaausrüstung. Dazu zählen z. B. in die Breitband-Kommunikationsgeräte von Linksys, DTVs und Unterhaltungssysteme von Sony, DVD-Recorder von Pioneer, digitale Settop-Boxen von Motorola, Netzwerk-Router von Cisco, 32-bit Mikrocontroller von Microchip Technology und Laserdrucker von Hewlett-Packard. MIPS Technologies wurde 1998 gegründet, hat seinen Hauptsitz in Sunnyvale, Kalifornien, und unterhält Büros in der ganzen Welt.

Folgen Sie MIPS auf Facebook, LinkedIn, YouTube, RSS and Twitter.

MIPS, MIPS32, MIPS64 und MIPS-Based sind Handelsmarken von MIPS Technologies Inc. in den Vereinigten Staaten und weiteren Ländern. Alle anderen Handelsmarken sind im Besitz ihrer jeweiligen Eigentümer.

Agentur Lorenzoni GmbH, Public Relations

Beate Lorenzoni-Felber

Landshuter Straße 29

85435 Erding

beate(at)lorenzoni.de

+49 8122 55917-0

http://www.lorenzoni.de

Datum: 10.05.2012 - 15:40 Uhr

Sprache: Deutsch

News-ID 635968

Anzahl Zeichen: 0

Kontakt-Informationen:

Ansprechpartner: Jen Bernier

Stadt:

USA

Telefon: +1 (408) 530 5178

Kategorie:

Telekommunikation

Anmerkungen:

Dieser Fachartikel wurde bisher 114 mal aufgerufen.

Der Fachartikel mit dem Titel:

"MIPS Technologies stellt neue Mikroprozessor-Cores der Aptiv(TM)-Generation vor"

steht unter der journalistisch-redaktionellen Verantwortung von

MIPS Technologies (Nachricht senden)

Beachten Sie bitte die weiteren Informationen zum Haftungsauschluß (gemäß TMG - TeleMedianGesetz) und dem Datenschutz (gemäß der DSGVO).